ICBN 2004, Kobe, Japan

# Bandwidth Allocation with Processing Constraints

April 8, 2004

Song Chong KAIST song@ee.kaist.ac.kr

# **Outline**

- Introduction

- □ Resource Allocation Principle

- System Model

- □ Flow Control Algorithm

- Equilibrium, Fairness & Stability

- □ IXP1200 Implementation & Performance Results

- Conclusion

- References

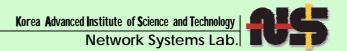

#### □ The evolution of router architecture

GPP-based architecture

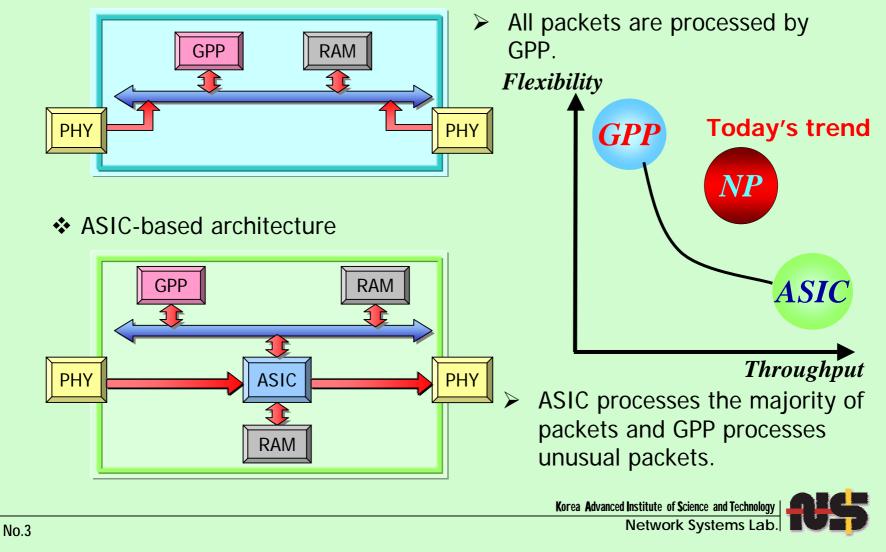

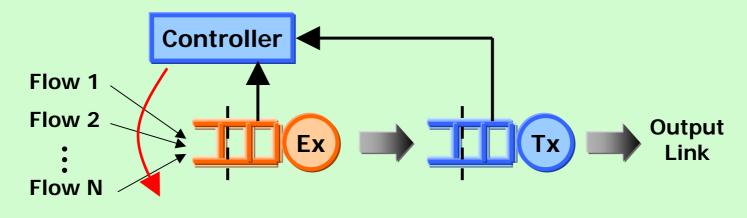

#### □ Logical architecture of a general NP-based node [Johnson 2002]

A network processor is mainly used for packet processing which includes CRC check, routing table look-up, header modification, and other extra processes for various network services and algorithms.

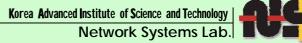

□ Network BW & silicon speed growth [Herity 2001]

- CPU speed : X 2.7 / 3year (by Moore's Law)

- Link capacity : X 4 / 3year

Hard to predict which resource to be bottlenecked !!

Korea Advanced Institute of Science and Technology Network Systems Lab.

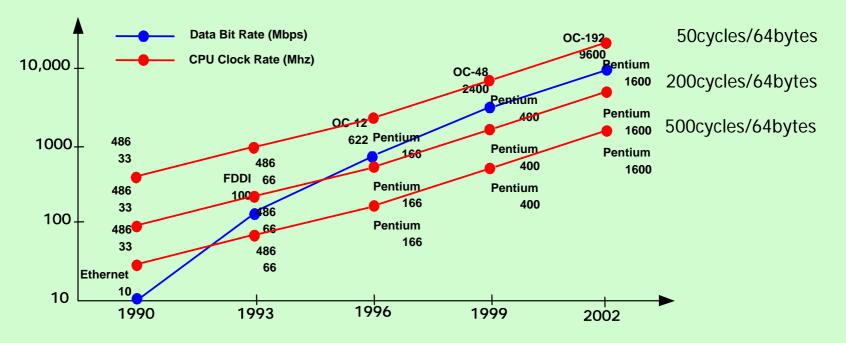

- □ Two-dimensional paradigm in flow control

- Should consider both processing resource and bandwidth resource.

- Hard to know the flow demand on processing resource until the processing completes.

- ✤ Can control flows only in terms of "bytes/sec".

### **Packet Processing**

- CommBench [9]: A telecommunications benchmark for network processors

- Header processing applications (HPA)

- RTR: lookup on tree data structures

- FRAG: header modifications and checksum

- DRR: packet scheduling

- TCP: pattern matching on header fields

- Payload processing applications (PPA)

- CAST: encryption/decryption

- ZIP: data compression

- ✤ REED: forward error correction (FEC)

- JPEG: media transcoding (DCT, Huffmann coding)

| HPA  | 64   | 576 | 1536 | (bytes) |

|------|------|-----|------|---------|

| ТСР  | 10.3 | 1.2 | .4   |         |

| FRAG | 7.7  | .9  | .3   |         |

| DRR  | 4.1  | .5  | .2   |         |

| ТСР  | 2.1  | .2  | .1   |         |

(instructions per byte)

| PPA  | enc | dec  |  |

|------|-----|------|--|

|      |     |      |  |

| REED | 603 | 1052 |  |

| ZIP  | 226 | 35   |  |

| CAST | 104 | 104  |  |

| JPEG | 81  | 60   |  |

(instructions per byte) Korea Advanced Institute of Science and Technology

### **Previous Work**

□ "Fair Resource Allocation in Active Networks" [Ramachandra 2000]

#### \* Fairness:

$\succ$  "CPU\_allocation(i) + BW\_allocation(i)" is to be equalized.

#### Weakness:

- Two-stage DRR scheduling

- Per-flow queueing

- ➢ No buffer control

Complex Not scalable Internal loss

Korea Advanced Institute of Science and Technology

Network Systems Lab.

# **Our Approach**

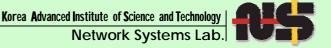

#### Fairness

- ✤ If BW > CPU, allocate CPU MAX-MIN fair rate.

- ✤ If BW < CPU, allocate BW MAX-MIN fair rate.</p>

- Otherwise, allocate the weighted average of above two rates.

#### Control

- ✤ FIFO queueing

- ✤ No per-flow queueing

- Joined control of rate & queue length

Simple

Scalable

No internal loss

#### **Resource Allocation Principle**

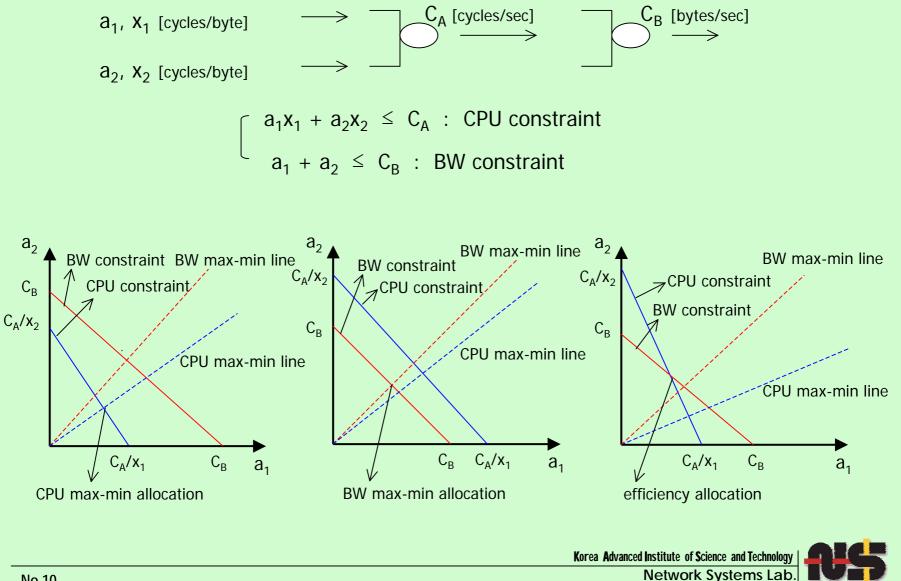

## **System Model**

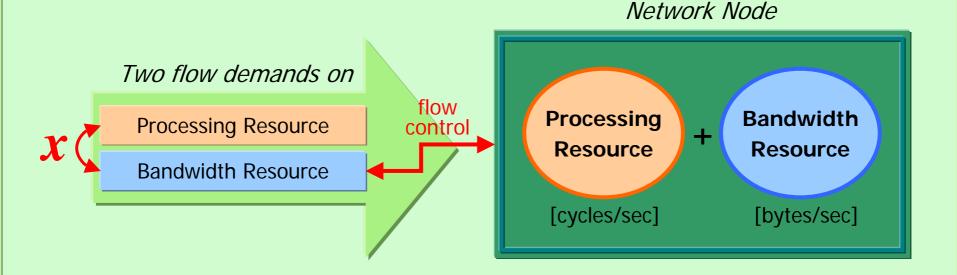

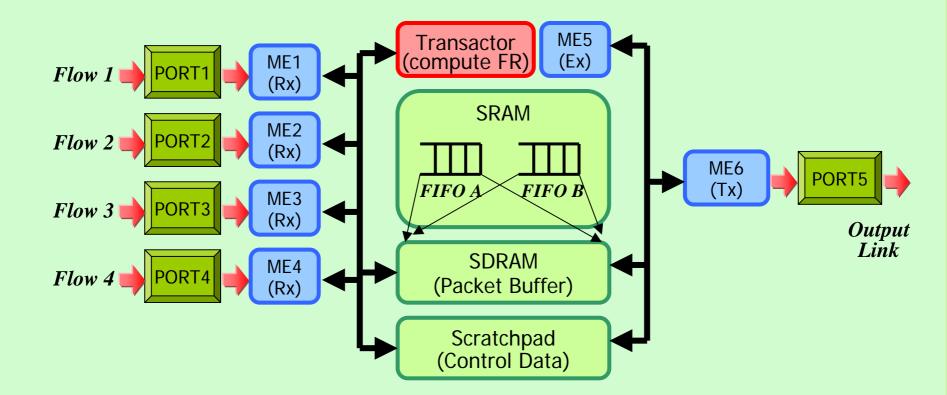

□ System model of a NP-based node employing the proposed approach

- Injected flow rate :  $a_i[k] = min(p_i, r_i[k])$

- Processing density : X<sub>i</sub>

(the only per-flow state)

demand for processing resource demand for bandwidth resource

> Korea Advanced Institute of Science and Technology | Network Systems Lab.

[cycles/byte]

# **Flow Control Algorithm**

❑ Processing density update : EWMA Filter

for every packet,

$$x_i = (1 - \alpha)x_i + \alpha \left(\frac{\text{processing time}}{\text{packet length}}\right)$$

$$(0 < \alpha < 1)$$

□ Fair rate (FR) is computed in two steps

Intermediate FR computation is based on PI control (BW MAX-MIN)

$$r[k] = \left[ r[k-1] - \frac{A}{|Q|} (q[k-1] - q[k-2]) - \frac{BT}{|Q|} (q[k-1] - q_T) \right]^+$$

$\mathbf{q}[\mathbf{k}]$  : total queue length (  $\mathbf{q}_{\mathbf{A}}[\mathbf{k}] + \mathbf{q}_{\mathbf{B}}[\mathbf{b}]$  )

$\boldsymbol{q}_T$  : target length of total queue

A,B : control gain

T : control period

${\it Q}$  : set of bottlenecked input flows (  $|{\sf Q}|$  is the cardinality of  ${\sf Q}$  )

# **Flow Control Algorithm**

Final FR computation (CPU MAX-MIN & BW MAX-MIN)

$$r_i[k] = \left(\frac{q_T - q_B[k-1]}{q_T}\right) \frac{\frac{1}{x_i}}{\sum_{i \in Q} \frac{1}{x_i}} |Q|r[k] + \left(\frac{q_B[k-1]}{q_T}\right) r[k], \quad \forall i \in N$$

- Intelligent behavior of the algorithm

- ✤ When processing resource is the bottleneck, allocate CPU MAX-MIN rate.

- ✤ When bandwidth resource is the bottleneck, allocate BW MAX-MIN rate.

- When both resources are bottlenecked together, determine the degree of bottleneck intensity of each resource and allocate rate as a convex combination of CPU MAX-MIN rate and BW MAX-MIN rate.

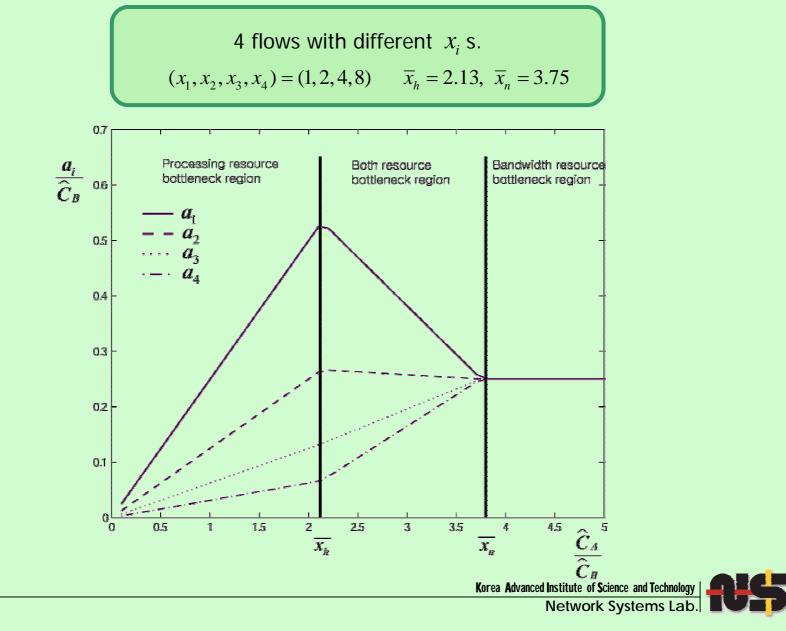

# **Steady State Solutions**

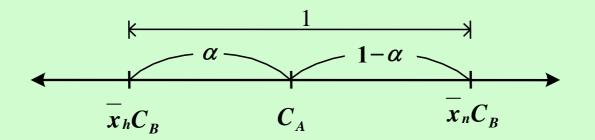

□ Three steady state solutions according to  $C_{A'}$ ,  $C_{B'}$  and the following two averages of  $x_i$ .

$$\overline{x}_{n} = \frac{\sum_{i \in Q} x_{i}}{|Q|} \quad \text{(numerical avg.)}, \qquad \overline{x}_{h} = \left(\frac{\sum_{i \in Q} \frac{1}{x_{i}}}{|Q|}\right)^{-1} \text{(harmonic avg.)}$$

♦ If  $C_A^* \ge \overline{x}_n C_B^*$  (bandwidth resource is the bottleneck),

$$q_A^*=0, \quad q_B^*=q_T, \quad a_i^*=rac{C_B}{N}$$

♦ If  $C_A^* \leq \overline{x}_h C_B^*$  (processing resource is the bottleneck),

$$q_A^* = q_T, \quad q_B^* = 0, \quad a_i^* = \frac{C_A}{Nx_i}$$

Korea Advanced Institute of Science and Technology Network Systems Lab.

#### **Steady State Solutions**

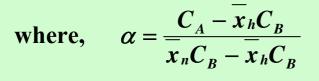

• If  $\overline{x}_h C_B^* < C_A^* < \overline{x}_n C_B^*$  (both resources are bottlenecked together),

$$q_A^* = (1-\alpha)q_T, \quad q_B^* = \alpha q_T, \quad a_i^* = (1-\alpha)\frac{\frac{1}{x_i}}{\sum_{i \in N} \frac{1}{x_i}}C_B + \alpha \frac{C_B}{N}$$

*a* determines the degree of bottleneck intensity.

#### Example

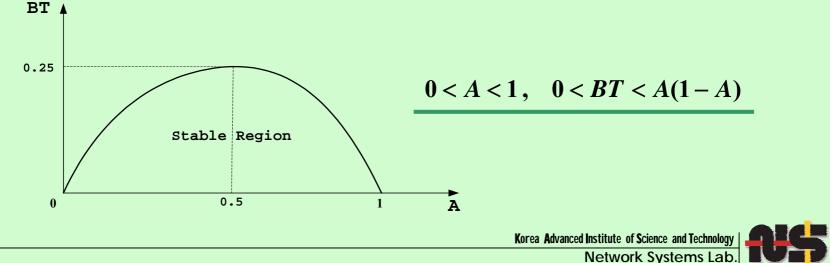

#### **Asymptotic Stability**

$\Box$  Error function :  $e[k] = q[k] - q_T$

□ Closed-loop difference equation of e[k]: e[k+1] - 2e[k] + (1 + A + BT)e[k-1] - Ae[k-2] = 0

□ Characteristic equation :  $z^3 - 2z^2 + (1 + A + BT)z - A = 0$

By Schűr-Cohn Stability Criteria [7], the closed-loop equation is asymptotically stable if and only if

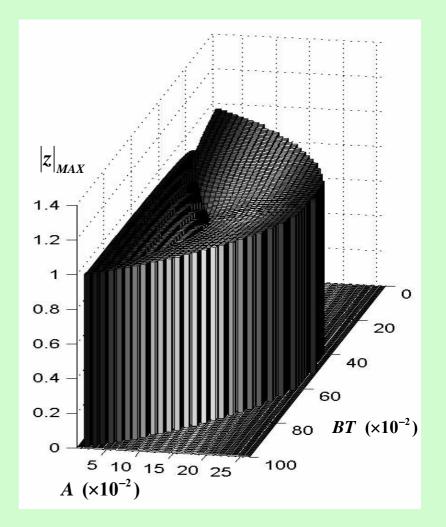

# **Asymptotic Decay Rate**

- Optimal gains

- Using numerical analysis,

A = 0.32BT = 0.05

✤ Asymptotic decay rate : 0.704 / T

# **Simulation Environment**

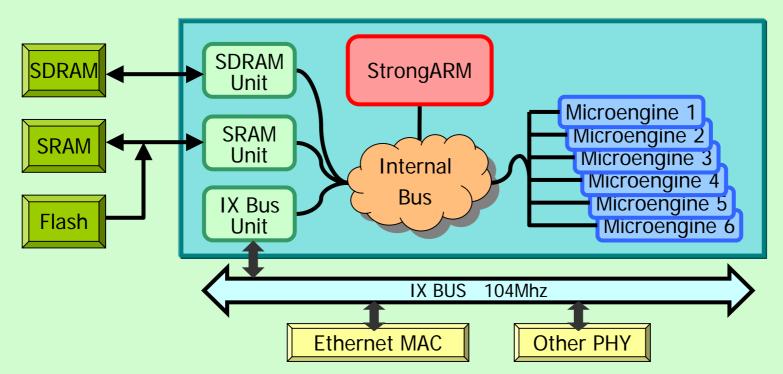

#### Intel IXP1200 Evaluation Platform [9]

- IXP1200 Network Processor

- Consists of one StrongARM Core(166Mhz) and six Microengines(166Mhz).

- Provides four hardware contexts with zero context switching overhead in each six microengine.

# **Simulation Environment**

□ Implemented IPv4 (RFC 1812) forwarding engine on ME5.

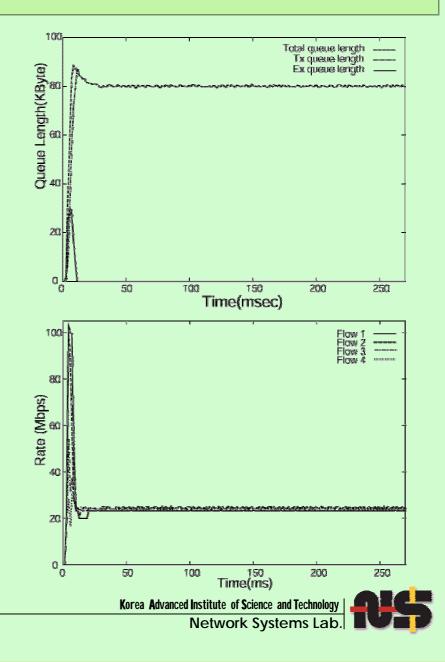

Bandwidth Resource Bottleneck Case

| Flow No. | x <sub>i</sub> | Fair Rate<br>(Mbps) | Actual Rate<br>(Mbps) |

|----------|----------------|---------------------|-----------------------|

| 0        | 2.5            | 25.0                | 23.2                  |

| 1        | 5.0            | 25.0                | 23.8                  |

| 2        | 10.0           | 25.0                | 24.4                  |

| 3        | 20.0           | 25.0                | 24.7                  |

| 3        | 20.0           | 25.0                | 24.7                  |

$C_B = 100 \text{ Mbps}$ Tx queue length : 80015 bytes Ex queue length : 0 bytes

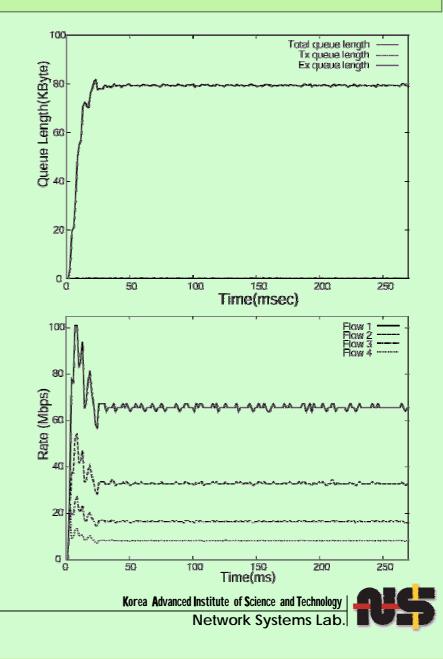

Processing Resource Bottleneck Case

| Flow No. | x <sub>i</sub> | Fair Rate<br>(Mbps) | Actual Rate<br>(Mbps) |

|----------|----------------|---------------------|-----------------------|

| 0        | 4.7            | 70.8                | 65.7                  |

| 1        | 9.4            | 35.4                | 32.9                  |

| 2        | 18.8           | 17.7                | 16.5                  |

| 3        | 37.5           | 8.9                 | 8.3                   |

$C_B = 300 \text{ Mbps}$ Tx queue length : 150 bytes Ex queue length : 79217 bytes

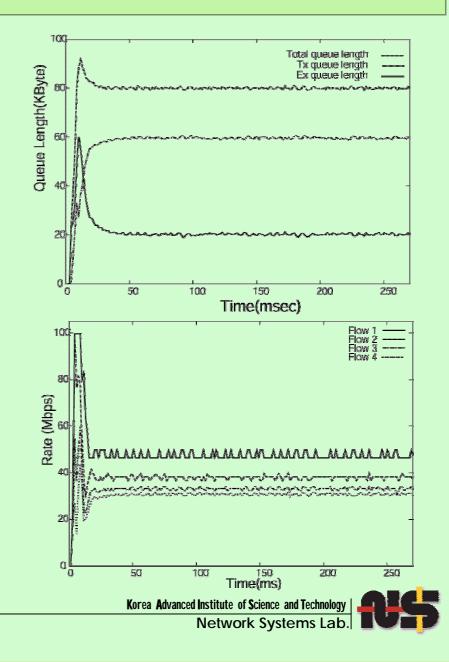

Both Resources Bottleneck Case I (BW is more bottlenecked:  $\alpha = 0.746$  )

| Flow No. | X <sub>i</sub> | Fair Rate<br>(Mbps) | Actual Rate<br>(Mbps) |

|----------|----------------|---------------------|-----------------------|

| 0        | 2.5            | 50.3                | 47.4                  |

| 1        | 5.0            | 40.1                | 37.9                  |

| 2        | 10.0           | 35.1                | 33.2                  |

| 3        | 20.0           | 32.5                | 30.8                  |

$C_B = 158 \text{ Mbps}$ Tx queue length : 56699 bytes Ex queue length : 20316 bytes

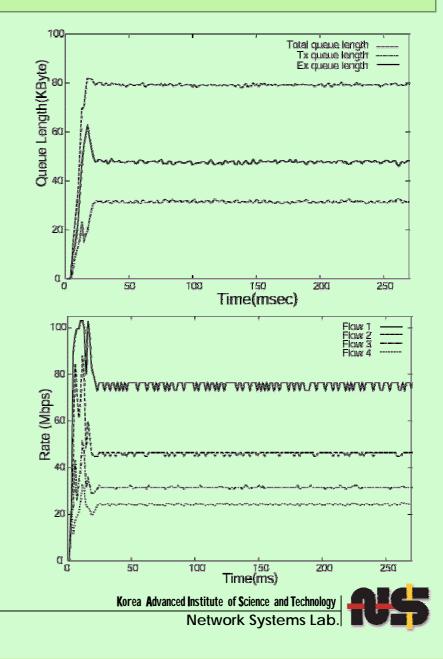

Both Resource Bottleneck Case II (CPU is more bottlenecked:  $\alpha = 0.393$ )

| Flow No. | x <sub>i</sub> | Fair Rate<br>(Mbps) | Actual Rate<br>(Mbps) |

|----------|----------------|---------------------|-----------------------|

| 0        | 2.5            | 78.4                | 75.3                  |

| 1        | 5.0            | 49.1                | 46.1                  |

| 2        | 10.0           | 34.4                | 31.5                  |

| 3        | 20.0           | 27.1                | 24.3                  |

$C_B = 189 \text{ Mbps}$ Tx queue length : 31441 bytes Ex queue length : 47703 bytes

# Conclusion

- □ Fair resource allocation when processing time is non-negligible

- New fairness characterization

- Control-theoretic algorithm

- Implementation of IP data path on IXP1200

#### Future work

- Distributed algorithm for a network of programmable nodes

- Understanding in optimization perspective

- Microscopic modeling of network processor architecture

- Joint management of bandwidth, processing and power

### References

- [1] D. Herity, "Network Processor Programming", Embeded Systems Programming, July 2001.

- [2] D. L. Tennenhouse, J. M. Smith, "A Survey of Active Network Research", IEEE Communications, 35(1):80-86, January 1997.

- [3] Vijay Ramachandran, "Fair Resource Allocation in Active Networks", *Computer Communications*, 2000.

- [4] Song Chong et. al, "A Simple, Scalable, and Stable Explicit Rate Allocation Algorithm for Max-Min Flow Control with Minimum Rate Guarantee", *IEEE/ACM Transactions on Networking*, Vol. 9, June 2001.

- [5] T. Spalink, S. Karlin, L. Peterson, "Building a Robust Software-Based Router Using Network Processors", *Proceedings of the 18th ACM Symposium on Operating Systems Principles(SOSP)*

- [6] Y.D. Lin, "DiffServ over Network Processors: Implementation and Evaluation", IEEE/Proceedings of the 10<sup>th</sup> Symposium on High Performance Interconnections Hot Interconnects, HotI 2002.

- [7] Erik J. Johnson and Aaron R. Kunze, "IXP1200 Programming", Intel Press, 2002.

- [8] IXP1200 Hardware Reference Manual

- [9] T. Wolf and M. Franklin, "CommBench A Telecommunications Benchmark for Network Processors"